Xilinx Ise Simulator

Xilinx ISE Simulator Xilinx ISE Simulator (also referred to as Xsim or Isim in some documentation) Weaning Yourself from Modelsim Xilinx and Modelsim parted ways a number of years ago which means it is no longer possible to install the Student Edition of Modelsim in our labs. However, the Xilinx tools have good built-in simulation capabilities and should run faster than the Student Edition of Modelsim. Before we get into details of using the Xilinx simulator, let us first discuss different versions of the Xilinx software. Xilinx Versions You may encounter multiple versions during your journey through FPGA Land. Xilinx ISE 9.2 - This is the version of Xilinx that we use in ECE 240 because it is the last version of ISE to support the Test Bench Waveform Editor. Xilinx ISE 14.7 - This is a much newer version of Xilinx that we use in ECE 440 in order to play with some of the more advanced capabilities. Xilinx Vivado - This is the latest and greatest (and the future) of Xilinx design tools.

Xilinx® ISE Simulator (ISim) VHDL Test Bench Tutorial Revision: February 27, 2010 215 E Main Suite D Pullman, WA 99163 (509) 334 6306 Voice and Fax. Xilinx Vivado - This is the latest and greatest (and the future) of Xilinx design tools. Sadly, a reasonably-priced FPGA platform is not yet available. Simulator Materials Xilinx ISE Quick Start Tutorial - This is for ISE 9.1 but it applies to 9.2 as well. It has a very brief, gentle intro to simulation, starting on p.

Sadly, a reasonably-priced FPGA platform is not yet available. Simulator Materials. This is for ISE 9.1 but it applies to 9.2 as well. It has a very brief, gentle intro to simulation, starting on p. However, it does not have much on the simulator commands and interface.

For that you need to fire up the simulator, from within ISE, and select Help from the menu at the top. This will bring up a set of HTML files that are stored locally on the drive as part of the installation. You can also browse these from outside the ISE environment by navigating to the appropriate folder. We have assembled a few, key pages to simplify your search.

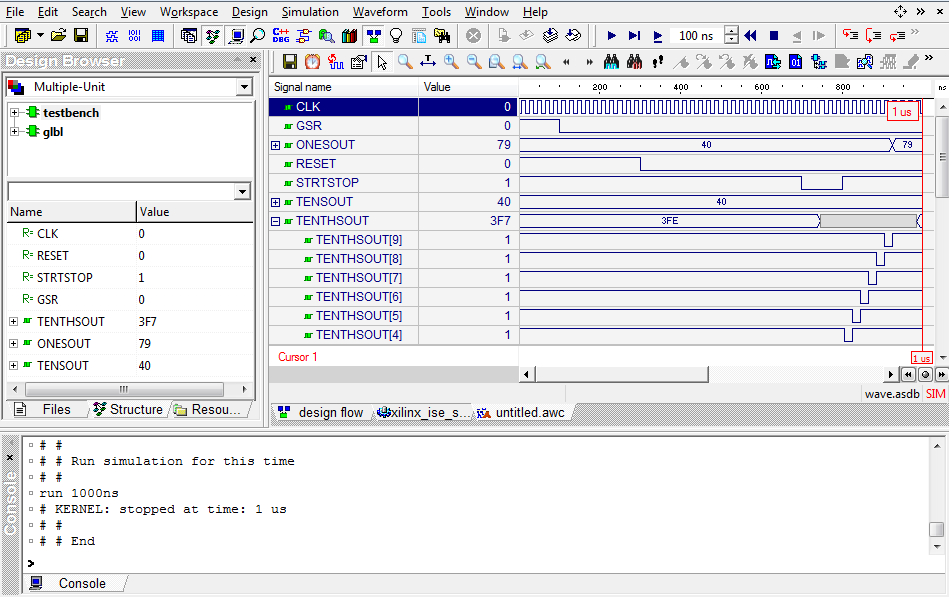

this is what you use to create the input stimulus. You may already be familiar with this. this page describes the layout of the simulation window. this page lists commands that can be typed into the console window. Most useful are restart and run.:-). this page is useful for drilling down through your hierarchy to view an internal signal, such as the state of an FSM, during behavioral simulation.

(after synthesis the design is flattened and internal signals often get minimized away). this is for 14.3, but not a bad start if you want more. this is the full manual for versions 14.3 through 14.7.

14.7 / October 23, 2013; 4 years ago ( 2013-10-23) Development status Superseded by, 6.1 Available in Website Xilinx ISE ( Integrated Synthesis Environment) is a software tool produced by for synthesis and analysis of designs, enabling the developer to ('compile') their designs, perform, examine diagrams, simulate a design's reaction to different stimuli, and configure the target device with the. Xilinx ISE is a design environment for FPGA products from Xilinx, and is tightly-coupled to the architecture of such chips, and cannot be used with FPGA products from other vendors. The Xilinx ISE is primarily used for circuit synthesis and design, while ISIM or the logic simulator is used for system-level testing.

Other components shipped with the Xilinx ISE include the Embedded Development Kit (EDK), a Software Development Kit (SDK) and ChipScope Pro. Since 2012, Xilinx ISE has been discontinued in favor of, that serves the same roles as ISE with additional features for development. Xilinx released the last version of ISE in October 2013 (version 14.7), and states that 'ISE has moved into the sustaining phase of its product life cycle, and there are no more planned ISE releases.' Contents.

Xilinx Ise Download Webpack

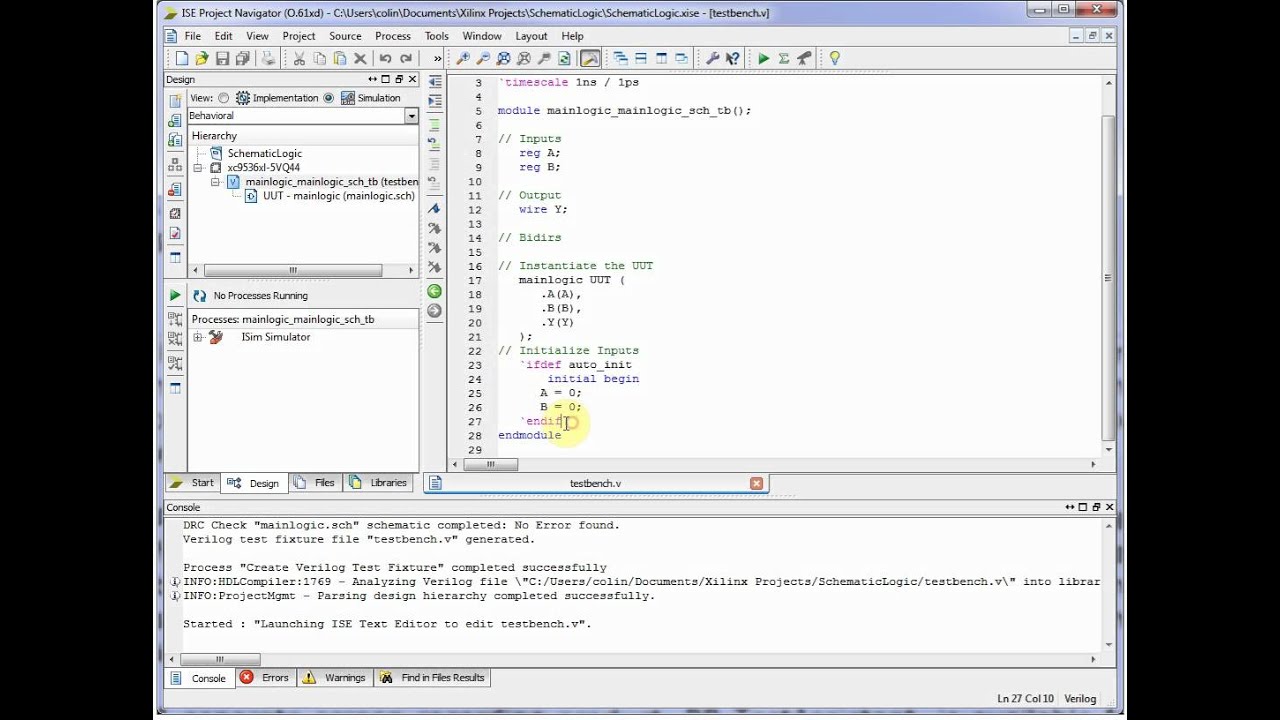

User Interface The primary user interface of the ISE is the Project Navigator, which includes the design hierarchy (Sources), a editor (Workplace), an output console (Transcript), and a processes tree (Processes). The Design hierarchy consists of design files (modules), whose dependencies are interpreted by the ISE and displayed as a. For single-chip designs there may be one main module, with other modules included by the main module, similar to the main subroutine in programs. Design constraints are specified in modules, which include pin configuration and mapping.

The Processes hierarchy describes the operations that the ISE will perform on the currently active module. The hierarchy includes compilation functions, their dependency functions, and other utilities.

The window also denotes issues or errors that arise with each function. The Transcript window provides status of currently running operations, and informs engineers on design issues. Such issues may be filtered to show Warnings, Errors, or both. Simulation System-level testing may be performed with ISIM or the logic simulator, and such test programs must also be written in HDL languages. Test bench programs may include simulated input signal waveforms, or monitors which observe and verify the outputs of the. Or ISIM may be used to perform the following types of simulations:.

Logical verification, to ensure the module produces expected results. Behavioural verification, to verify logical and timing issues. Post-place & route simulation, to verify behaviour after placement of the module within the reconfigurable logic of the FPGA Synthesis Xilinx's patented algorithms for synthesis allow designs to run up to 30% faster than competing programs, and allows greater logic density which reduces project time and costs. Also, due to the increasing complexity of FPGA fabric, including memory blocks and I/O blocks, more complex synthesis algorithms were developed that separate unrelated modules into slices, reducing post-placement errors. IP Cores are offered by Xilinx and other third-party vendors, to implement system-level functions such as (DSP), bus interfaces, networking protocols, and peripherals.

Download Lagu Armada Asal Kau Bahagia Bursa Lagu. Lagu Iklim Dermaga Saksi Bisu Download Lagu Mp3 Gerimis Melanda Hati D O W N L O A D L A G U. Video lagu armada pemilik hati. Download lagu Armada - Pemilik Hati MP3 dapat kamu download secara gratis di Planetlagu. Details lagu Armada - Pemilik Hati bisa kamu lihat di tabel, untuk link download Armada - Pemilik Hati berada dibawah. BURSALAGU - Free MP3 Download Lagu Terbaru Gratis Bursa Lagu - ARMADA Bursalagu Media Sharing Music Lagu Mp3 Review Album. Download mp3 lagu, download mp3 lagu indonesia, download mp3 lagu natal, download mp3 lagu barat, download mp3 lagu minang, download mp3 lagu lagu. Armada – Pemilik Hatimu LIRIK LAGU Pemilik Hatimu Lihat ku disini Kau buat ku menangis Tak ingin menyerah Tapi tak menyerah Mencoba lupakan Tapi ku bertahan.

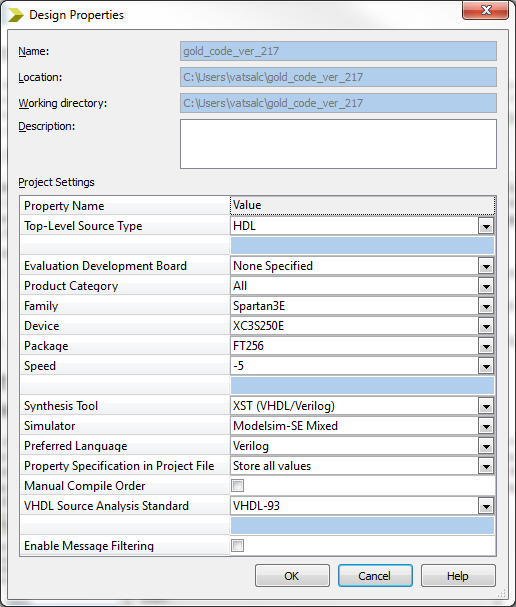

Xilinx has been instrumental in shifting designs from ASIC-based implementation to FPGA-based implementation. Editions The Subscription Edition is the licensed version of Xilinx ISE, and a free trial version is available for download. The Web Edition is the free version of Xilinx ISE, that can be downloaded and used for no charge.

It provides synthesis and programming for a limited number of devices. In particular, devices with a large number of I/O pins and large gate matrices are disabled. The low-cost Spartan family of is fully supported by this edition, as well as the family of, meaning small developers and educational institutions have no overheads from the cost of development software. License registration is required to use the Web Edition of Xilinx ISE, which is free and can be renewed an unlimited number of times.

^, Xilinx Downloads. (PDF). 100728 xilinx.com. ^, Springer Science & Business Media, 14-Nov-2007. ^, MIT Press, 2004., Springer Science & Business Media, 11-May-2012., Morgan Kaufmann, 10-Sep-2010., First version released in 2012, Xilinx Downloads., John Wiley & Sons, 20-Sep-2011. ^, Elsevier, 30-Apr-2004.

Xilinx Simulation Tutorial

100811 xilinx.com. (PDF). 100828 xilinx.com.

(PDF). Chapter 3: Architecture Support and Requirements: Xilinx, Inc. Gentoo Community.

Archived from on October 7, 2012. Retrieved 8 May 2012. Arch Community. Retrieved 8 May 2012. What's All This Brouhaha? Archived from on March 3, 2011.

Retrieved 8 May 2012. Koszek, Wojciech. Retrieved 8 May 2012. See also. External links Xilinx.

Installation.